MOS管介绍

在使用MOS管设计开关电源或者马达驱动电路的时候,一般都要考虑MOS的导通电阻,最大电压等,最大电流等因素。

MOSFET管是FET的一种,可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,一般主要应用的为增强型的NMOS管和增强型的PMOS管,所以通常提到的就是这两种。

这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。

在MOS管内部,漏极和源极之间会寄生一个二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要,并且只在单个的MOS管中存在此二极管,在集成电路芯片内部通常是没有的。

MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免。

MOS管导通特性

导通的意思是作为开关,相当于开关闭合。

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到一定电压(如4V或10V, 其他电压,看手册)就可以了。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

MOS开关管损失

不管是NMOS还是PMOS,导通后都有导通电阻存在,因而在DS间流过电流的同时,两端还会有电压,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几毫欧,几十毫欧左右

MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越快,导通瞬间电压和电流的乘积很大,造成的损失也就很大。降低开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。

MOS管驱动

MOS管导通不需要电流,只要GS电压高于一定的值,就可以了。但是,我们还需要速度。

在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电。对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大。选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小。

普遍用于高端驱动的NMOS,导通时需要是栅极电压大于源极电压。而高端驱动的MOS管导通时源极电压与漏极电压(VCC)相同,所以这时栅极电压要比VCC大(4V或10V其他电压,看手册)。如果在同一个系统里,要得到比VCC大的电压,就要专门的升压电路了。很多马达驱动器都集成了电荷泵,要注意的是应该选择合适的外接电容,以得到足够的短路电流去驱动MOS管。

Mosfet参数含义说明

Features:

Vds: DS击穿电压.当Vgs=0V时,MOS的DS所能承受的最大电压

Rds(on):DS的导通电阻.当Vgs=10V时,MOS的DS之间的电阻

Id: 最大DS电流.会随温度的升高而降低

Vgs: 最大GS电压.一般为:-20V~+20V

Idm: 最大脉冲DS电流.会随温度的升高而降低,体现一个抗冲击能力,跟脉冲时间也有关系

Pd: 最大耗散功率

Tj: 最大工作结温,通常为150度和175度

Tstg: 最大存储温度

Iar: 雪崩电流

Ear: 重复雪崩击穿能量

Eas: 单次脉冲雪崩击穿能量

BVdss: DS击穿电压

Idss: 饱和DS电流,uA级的电流

Igss: GS驱动电流,nA级的电流.

gfs: 跨导

Qg: G总充电电量

Qgs: GS充电电量

Qgd: GD充电电量

Td(on): 导通延迟时间,从有输入电压上升到10%开始到Vds下降到其幅值90%的时间

Tr: 上升时间,输出电压 VDS 从 90% 下降到其幅值 10% 的时间

Td(off): 关断延迟时间,输入电压下降到 90% 开始到 VDS 上升到其关断电压时 10% 的时间

Tf: 下降时间,输出电压 VDS 从 10% 上升到其幅值 90% 的时间 ( 参考图 4) 。

Ciss: 输入电容,Ciss=Cgd + Cgs.

Coss: 输出电容,Coss=Cds +Cgd.

Crss: 反向传输电容,Crss=Cgc.

MOSFET栅极驱动的优化设计

1 概述

MOS管的驱动对其工作效果起着决定性的作用。设计师既要考虑减少开关损耗,又要求驱动波形较好即振荡小、过冲小、EMI小。这两方面往往是互相矛盾的,需要寻求一个平衡点,即驱动电路的优化设计。驱动电路的优化设计包含两部分内容:一是最优的驱动电流、电压的波形;二是最优的驱动电压、电流的大小。在进行驱动电路优化设计之前,必须先清楚MOS管的模型、MOS管的开关过程、MOS管的栅极电荷以及MOS管的输入输出电容、跨接电容、等效电容等参数对驱动的影响。

2 MOS管的模型

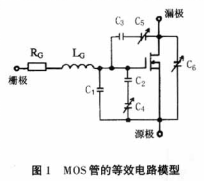

MOS管的等效电路模型及寄生参数如图1所示。图1中各部分的物理意义为:

(1)LG和LG代表封装端到实际的栅极线路的电感和电阻。

(2)C1代表从栅极到源端N+间的电容,它的值是由结构所固定的。

(3)C2+C4代表从栅极到源极P区间的电容。C2是电介质电容,共值是固定的。而C4是由源极到漏极的耗尽区的大小决定,并随栅极电压的大小而改变。当栅极电压从0升到开启电压UGS(th)时,C4使整个栅源电容增加10%~15%。

(4)C3+C5是由一个固定大小的电介质电容和一个可变电容构成,当漏极电压改变极性时,其可变电容值变得相当大。

(5)C6是随漏极电压变换的漏源电容。

MOS管输入电容(Ciss)、跨接电容(Crss)、输出电容(Coss)和栅源电容、栅漏电容、漏源电容间的关系如下:

3.MOS管的开通过程

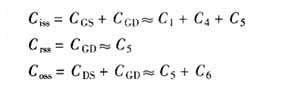

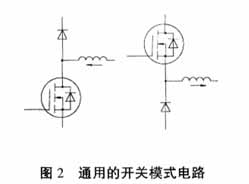

开关管的开关模式电路如图2所示,二极管可是外接的或MOS管固有的。开关管在开通时的二极管电压、电流波形如图3所示。在图3的阶段1开关管关断,开关电流为零,此时二极管电流和电感电流相等;在阶段2开关导通,开关电流上升,同时二极管电流下降。开关电流上升的斜率和二极管电流下降的斜率的绝对值相同,符号相反;在阶段3开关电流继续上升,二极管电流继续下降,并且二极管电流符号改变,由正转到负;在阶段4,二极管从负的反向最大电流IRRM开始减小,它们斜率的绝对值相等;在阶段5开关管完全开通,二极管的反向恢复完成,开关管电流等于电感电流。

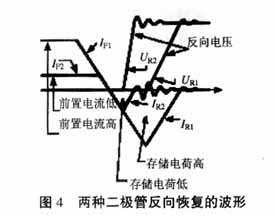

图4是存储电荷高或低的两种二极管电流、电压波形。从图中可以看出存储电荷少时,反向电压的斜率大,并且会产生有害的振动。而前置电流低则存储电荷少,即在空载或轻载时是最坏条件。所以进行优化驱动电路设计时应着重考虑前置电流低的情况,即空载或轻载的情况,应使这时二极管产生的振动在可接受范围内。

4 栅极电荷QG和驱动效果的关系

栅极电荷QG是使栅极电压从0升到10V所需的栅极电荷,它可以表示为驱动电流值与开通时间之积或栅极电容值与栅极电压之积。现在大部分MOS管的栅极电荷QG值从几十纳库仑到

两百纳库仑。

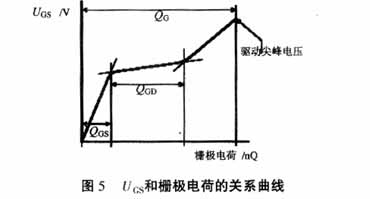

栅极电荷QG包含了两个部分:栅极到源极电荷QGS;栅极到漏极电荷QGD—即“Miller”电荷。QGS是使栅极电压从0升到门限值(约3V)所需电荷;QGD是漏极电压下降时克服“Miller”效应所需电荷,这存在于UGS曲线比较平坦的第二段(如图5所示),此时栅极电压不变、栅极电荷积聚而漏极电压急聚下降,也就是在这时候需要驱动尖峰电流限制,这由芯睡内部完成或外接电阻完成。实际的QG还可以略大,以减小等效RON,但是太大也无益,所以10V到12V的驱动电压是比较合理的。这还包含一个重要的事实:需要一个高的尖峰电流以减小MOS管损耗和转换时间。

重要是的对于IC来说,MOS管的平均电容负荷并不是MOS管的输入电容Ciss,而是等效输入电容Ceff(Ceff=QG/UGS),即整个0<UGS<UGS(th)的等效电容,而Ciss只是UGS=0时的等效电容。

漏极电流在QG波形的QGD阶段出现,该段漏极电压依然很高,MOS管的损耗该段最大,并随UDS的减小而减小。QGD的大部分用来减小UDS从关断电压到UGS(th)产生的“Miller”效应。QG波形第三段的等效负载电容是:

5 优化栅极驱动设计

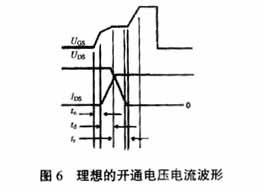

在大多数的开关功率应用电路中,当栅极被驱动,开关导通时漏极电流上升的速度是漏极电压下降速度的几倍,这将造成功率损耗增加。为了解决问题可以增加栅极驱动电流,但增加栅极驱动上升斜率又将带来过冲、振荡、EMI等问题。优化栅极驱动设计,正是在互相矛盾的要求中寻求一个平衡点,而这个平衡点就是开关导通时漏极电流上升的速度和漏极电压下降速度相等这样一种波形,理想的驱动波形如图6所示。

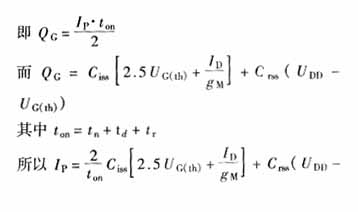

图6的UGS波形包括了这样几部分:UGS第一段是快速上升到门限电压;UGS第二段是比较缓的上升速度以减慢漏极电流的上升速度,但此时的UGS也必须满足所需的漏极电流值;UGS第四段快速上升使漏极电压快速下降;UGS第五段是充电到最后的值。当然,要得到完全一样的驱动波形是很困难的,但是可以得到一个大概的驱动电流波形,其上升时间等于理想的漏极电压下降时间或漏极电流上升的时间,并且具有足够的尖峰值来充电开关期间的较大等效电容。该栅极尖峰电流IP的计算是:电荷必须完全满足开关时期的寄生电容所需。

UG(th))

UG(th))

6 应用实例

在笔者设计的48V50A电路中采用双晶体管正激式变换电路,其开关管采用IXFH24N50,其参数为:

根据如前所述,驱动电压、电流的理想波形不应该是一条直线,而应该是如图6所示的波形。实验波形见图7。

7 结论

本文详细介绍了MOS管的电路模型、开关过程、输入输出电容、等效电容、电荷存储等对MOS管驱动波形的影响,及根据这些参数对驱动波形的影响进行的驱动波形的优化设计实例,取得了较好的实际效果。

影响MOSFET开关速度除了其本身固有Tr,Tf外,还有一个重要的参数:Qg (栅极总静电荷容量).该参数与栅极驱动电路的输出内阻共同构成了一个时间参数,影响着MOSFET的性能(你主板的MOSFET的栅极驱动电路就集成在IRU3055这块PWM控制芯片内); r6 @0 k" S/ l3 }4 u, r/ W

厂家给出的Tr,Tf值,是在栅极驱动内阻小到可以忽略的情况下测出的,实际应用中就不一样了,特别是栅极驱动集成在PWM芯片中的电路,从PWM到MOSFET栅极的布线的宽度,长度,都会深刻影响MOSFET的性能.如果PWM的输出内阻本来就不低,加上MOS管的Qg又大,那么不论其Tr,Tf如何优秀,都可能会大大增加上升和下降的时间![]()

偶认为,BUCK同步变换器中,高侧MOS管的Qg比RDS等其他参数更重要,另外,栅极驱动内阻与Qg的配合也很重要,一定 程度上就是由它的充电时间决定高侧MOSFET的开关速度和损耗..![]()

看从哪个角度出发。电荷泻放慢,说明时间常数大。时间常数是Ciss与Rgs的乘积。栅源极绝缘电阻大,说明制造工艺控制较好,材料、芯片和管壳封装的表面杂质少,漏电少。时间常数大,栅源极等效输入电容也大。栅源极等效输入电容,与管芯尺寸成正比并与管芯设计有关。通常,管芯尺寸大,Ron(导通电阻)小、跨导(增益)大。栅源极等效电容大,会增加开关时间、降低开关性能、降低工作速度、增加功率损耗。Ciss与电荷注入率成正比,可能还与外加电压有关并具有非线性等。以上,均是在相同条件下的对比。从应用角度出发,同等价格,多数设计希望选用3个等效电容(包括Ciss)小的器件。Ciss=Cgd+Cgs,充放电时间上也有先后,先是Cgs充满,然后是Cgd.

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。